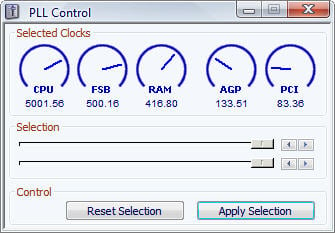

@=RvE=Paploo ClockGen should at least be able to read the values of your PLL. In the 'PLL Setup' window select 'not specified' from the drop-list, then click on 'Read Clocks', make a screenshot of. Posted on November 27, 2012 by tiswan senjaya - wordpress blog. ClockGen merupakan tool portable overclock IC PLL seperti SetFSB, SpeedFan dan SysTool. Jendela yang sederhana terdiri dari Option, PLL Setup, PLL Control dan Clock. Option: Untuk menyimpan profile setingan. The reference clock (upper left two topmost pins) is manipulated internally in a phase lock loop (PLL center) to generate a frequency for the output dividers (FOD 1-4). These output dividers then set the frequencies for their respective clock outputs. Stata 13 mp serial number code authorization. ClockGen 1.0.5.3. Once you get your PLL model selected, click on 'Read Clocks', then open the 'PLL Control' window. Notice that the number of sliders depends on the PLL model features. Some models also only support a predefined set of frequencies, and therefore may show a 'step-by-step' slider. Once your new clocks are choosen, clock on 'Apply.

SetFSB is a useful system information tool which may allow you to increase the clock rate of your processor. Buku ajar fisiologi kedokteran ganong pdf. With that in mind, SetFSB is designed and intended for advanced users only as misuse may cause physical damage to your hardware!

As the name suggests, SetFSB allows users with certain chips to modify their FSB speed without having to access it from the system BIOS menu. This can be useful to users of certain PC hardware whose manufacturer has disable advanced system menus Brambach baby grand piano serial number.

Within the application layout are details about your DDR RAM, FSB, AGP and PCI cards; You may modify them with the relevant sliders when possible. One thing that SetFSB won't modify are voltage values or graphics processors.

SetFSB 2.2.134.98 on 32-bit and 64-bit PCs

This download is licensed as freeware for the Windows (32-bit and 64-bit) operating system on a laptop or desktop PC from drivers without restrictions. SetFSB 2.2.134.98 is available to all software users as a free download for Windows.

Clockgen Pll Setup Download

Filed under:- SetFSB Download

- Freeware Drivers

- Major release: SetFSB 2.2

zodttd

New Member

Clockgen Pll Setup Download Windows 10

EDIT:

I was able to successfully try out cunningd46's method of overclocking the Clevo M570U based notebook. It's very simple. Just download ClockGen at http://www.cpuid.com/clockgen.php (currently v1.0.5.3) and:

1. Choose the PLL from the PLL SETUP menu and select ICS 950405

2. Checkmark the IGNORE PCI/AGP.

3. Click READ CLOCKS.

4. The 9th byte of the PLL OUTPUT is most likely set to 7E. Change it to 7F. Click UPDATE then APPLY.

5. Now you are able to overclock via PLL CONTROL by simply sliding the bar (fine tuned).

THANKS SO MUCH CUNNINGD46!

Also, for those who like to overclock, keep in mind you can set a high overclock and keep cool by only using it when needed by CPU load based throttling enabled with RMClock at www.rightmark.com. Be sure to turn off C/G states power maangement in the BIOS first.

Original posting:

Hi everyone,

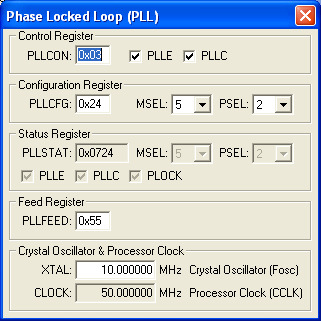

I've been studying PLL's on the Clevo M570U. I determined the PLL is by ICS/IDT and follows the CK410M standard and seems to work with ICS 954204 bitsets.

So assuming its a ICS 954204 I've been able to change the frontside bus via Clockgen/SetFSB by editing the PLL registers directly.

Here's what you need to do to change the registers on the ics954204 via ClockGen:

1. Run clockgen and select ICS954119 within PLL Setup

2. Click Read Clocks

3. In IC Dump you should see the following bytes (or very similar):

3E FF F9 00 04 44 8B 11 3C 7E 15

CA 3C E6 3B 00 9D 61 08 D5 34

FSB Table:

0 0 0 266.67 100.00 33.33 14.318 48.00 96.00

0 0 1 133.33 100.00 33.33 14.318 48.00 96.00

0 1 0 200.00 100.00 33.33 14.318 48.00 96.00

0 1 1 166.67 100.00 33.33 14.318 48.00 96.00

1 0 0 333.33 100.00 33.33 14.318 48.00 96.00

1 0 1 100.00 100.00 33.33 14.318 48.00 96.00

1 1 0 400.00 100.00 33.33 14.318 48.00 96.00

1 1 1 200.00 100.00 33.33 14.318 48.00 96.00

To change the FSB according to ICS954204.pdf:

1. In ClockGen select the byte06 (8B) in the IC Dump.

2. Change the binary value to 10001xxx where xxx is the first three digits in the above FSB table.

Currently I can only change the FSB to:

133.33 (001)

166.67 (011)

100.00 (101)

This may be due to my RAM or other components. I'd like to know if someone can reach higher than the stock 166.67 FSB, especially at 11x multiplier!

Tips to help those who try this:

The byte06 (8B) bitset has test features built in to lower the FSB a bit which might help. To do this enable the following bits by setting them to 1: 111xxxxx

The byte01 (FF) can be change to FE to disable spread spectrum.

The spread spectrum is controlled by the byte09 (7E).

So in short I've been able to change the frontside bus but not higher than the normal 166.67 speed. For those who might be able to reach about 190MHz FSB, you're in luck for sure. I have a feeling the PCI/PCI-E/SATA isn't being locked and that's why I can't reach a higher FSB.

For those who are worried about trying this, there is a risk of turning your computer into a brick. My computer works fine and all I need to do when I set the PLL to a wrong state was reboot. I did my tests with C states turned off in the BIOS.

For the complete datasheet for the ICS 954204 goto: http://www.idt.com/products/files/2537897/ics954204.pdf

Hope this helps someone, and can help me reach a higher FSB for the love of overclocking.